????????������Ƶ����(A2B?)�ڽڵ�֮�����Ӷ�ͨ��I2Sͬ��PCM����,����ɴ�15�ס�������I2S��ͬ����ʱ�ֶ�·����(TDM)������չ��һ�����Ӷ���ڵ��ϵͳ,����ÿ���ڵ����ʹ�����ݡ��ṩ����,�������С�

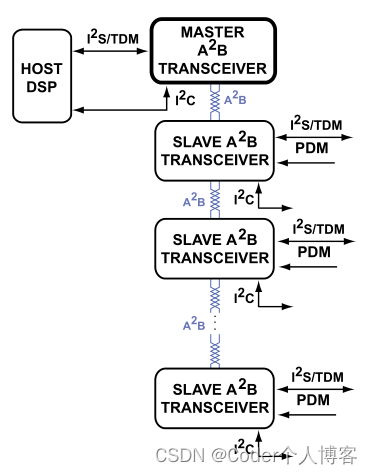

????????�շ���֧����ЩA2B����,ͨ����ͨ��I2S/TDM�ӿ���ͨ�������źŴ�����(dsp)���ֳ��ɱ��������(fpga)��ר�ü��ɵ�·(asic)����˷硢ģ��ת����(adc)������ģ��ת����(dac)�ͱ������ֱ�ӽӿڡ����ǻ��ṩ��һ��PDM�ӿ�,��ֱ�����Ӷ��4��PDM������˷硣����A2B���߹���(����)����,ͨ��ͨ����·ʹ�õ���ͬ�ij�����˫������ӽڵ㹩���ѹ�͵��������շ�������ȫ֧��ͨ��A2B��·����I2Cͨ�š�

????????�շ������������ص�:

??????????????? 1����·����:

??????????????? ????????1.1��������ӡ�

??????????????? ????????1.2���ڵ������ε�����(UTP)��������(���³����Բ�Ʒ���ݱ�Ϊ)��

??????????????? 2��Զ����ͨ��:

??????????????????????? 2.1������ͬ��:

????????????????????????????????��ͨ��I2S/TDM��I2S/TDM�ӿڡ�

????????????????????????????????ͬ��,���нڵ�ͬ��ʱ�ӡ�

????????????????????????????????���ӳٴӻ����ӻ�ͨ�š�

??????????????????????? 2.2��I2C��I2C���ƺ�״̬��Ϣ��

??????????????? ????????2.3��Զ����GPIO��

??????? ????????3����ʹ��SigmaStudioTMͼ�ο������߽������á�

??????????????? 4���ʺ�����Ӧ�á�

??????????????? 5��������ΪA2B���������ӽӿڡ�

??????????????? 6��I2C�ӿڡ�

??????? ????????7��8λ~ 32λ��ͨ��I2S/TDM�ӿڡ�

??????????????? ????????7.1��I2S/TDM/PDM�ɱ���������ʡ�

??????????????? ????????7.2�����32·(1 �� TDM32��2 �� TDM16),����ӳ��32��������A2B���߲�λ��

??????? ????????8��PDM����֧�ֶ��4���߶�̬��Χ����˷硣

??????????????? 9��ÿ���շ�����ΨһID�Ĵ���?֧�ֽ����ֱͨ���ߡ�

??????? ????????10���ɱ������,���Ż�EMC���ܡ�

1��A2B����

????????Ϊ�˸��õ�����A2Bϵͳ,���������������а����ġ�

????????A-Side or A-Port:A2B�շ����ӿ�,����master(�������νڵ�)��

????????B-Side or B-Port:A2B�շ����ӿ�,�������һ��ֱ�д�����(�����ε���һ��ֱ�д�����)��

????????Bus Link:A2B���߿����ɶ��������ʽ�Ĵӽڵ����ӵ��������ڵ㡣���ڵ�ʹӽڵ�0֮�����������,�Լ��ӽڵ�֮�����������A2B����,��Ϊ������·��ÿ��ĸ��ͨ��ʹ��һ�Է����ε�˫���ߡ�

????????Data Channel:����ͨ��Ϊ����������/ִ����(��ADC����˷硢��������)����I2S/TDMͬ�����ݡ�I2S/TDM�ӿ�ʹ����ͬ��С������ͨ��,���������ֵĿ���ͨ��С��I2S/TDM����ͨ���Ŀ��ȡ��շ�����I2S/TDM�ӿ�֧��16��32λ�ɱ������ͨ�����ȡ�

????????Data Slot:ӳ�䵽A2B�����ϵĵ���������/ִ����(����ADC����˷��������)��ͬ�������֡�

????????Downstream:ͨ���������ڵ�����ӽڵ�,��ֹ�����һ�������ӽڵ㡣

????????Host:Ϊ���շ�����̵Ĵ�����������Ҳ��A2B�����ϵ�ͬ��ʱ��Դ��ʱ���ź�(BCLK)������������֮��I2S/TDM�ӿڵ�һ���֡�

??????? I2S/TDM:I2S (inter IC sound)������PCB�ϵ���ƵоƬ֮�䴫������������(PCM)��Ϣ��I2S/TDM�ӿ�ʹ��ʱ�ָ���(TDM)��I2S������(2ͨ��)������չ�����ͨ����

????????Local Power:��ʹ��A2B���ߵ�Դ�Ĵӽڵ�ʹ���ɶ�����ṩ�ı��ص�Դ��

????????LVDS:�͵�ѹ���źš�

????????Master Node:ʱ�ӵķ�����(Դ��I2S����)���������ݡ�������ƺ͵�Դ�����ڵ���������������A2B���շ������,A2B���շ�������������������Ч�غɲ�����Ч�غɷ���������

????????PDM:�����ܶȵ���(PDM)����sigma�任����PDM��ʽ��ʾ��ȡǰ�Ĺ�����1λ�� �� ADC�ź�,������������˷�������ʽ��

????????Phantom Power:�ӽڵ���Խ��뵽A2B������·�ϵ�ƫ�õ�ѹ,��������ΪΨһ�ĵ�Դ��������A2B���߹���Ĵӽڵ㱻��Ϊ�ǡ��鹩�硱��

????????PRBS:α����������С�

????????Preamble:��ʾ����֡����Ӧ֡��ʼ��ͬ��λ������ÿ������֡,���ض˶��������ο���֡�����ԡ����շ��������ο���ǰ��ͬ��,�����в���һ�����صġ���λһ�µ���ʱ�ӡ�

????????Response Time:ָ�����һ���ڵ��ڳ�֡������ȴ���ʱ��,�ýڵ�����Ӧͬ����Ӧ֡(SRF)֮ǰ����Ӧʱ�������ڵ�������ڵ���������дӽڵ��б��,�Ա���Щ�ڵ�֪����ʱ�����������л������Ρ�

????????Slave Node:��Ѱַ�������ӵ㡣�ӽڵ���������κ��������ݲ۵�Դ��/��Ŀ�ĵء�ÿ��A2B�ӽڵ㶼��һ��A2B���շ�����

????????Synchronization Control and Response Frames (SCF/SRF):�ڵ�Ŀ���֡(���Ʊ�ͷ)�ͽڵ����Ӧ֡(��Ӧ��ͷ)��ͷ����һ������ͬ����ǰ��,�����������нڵ���ж�д���ʡ�

????????Synchronous Data:�����Թ̶���ʱ����(����44.1 kHz��48 kHz֮��ѡ��)�������䵽ͬһ���ڵ�,����ͬһ���ڵ㴫������(������Ƶ�ź�)��

????????Superframe:�����ܽṹΪA2B������SCF��ʼ,������ѡ�����ݲ�,����SRF����������֡ÿ1024������ʱ�������ظ�һ�Ρ�

????????Upstream:ͨ���������һ�еĴӽڵ㵽���ڵ㡣

2��A2B����ϸ��

????????ͨ��ϵͳ��ͼ��ʾ����һ��A2Bͨ��ϵͳ,����һ��������ӵ�ϵͳ,���շ������������ơ�I2S/TDM�ӿ��ϵ�������ʱͬ����ͬ���ź�(SYNC),Ƶ��Ϊ44.1 kHz ~ 48khz,����A2B�ڵ�ͬ������Ƶ�ʡ���A2B�����ϵ�ͨ������������������Եij���֡�з��������ݴ�����õ���A2Bϵͳ����ʱ��(SYSBCLK)����,�ȳ�֡����(48khzʱ49.152 MHz, 44.1 kHzʱ45.158 MHz)��1024����ÿ����֡����Ϊ���δ��䡢���δ��������(����δ������)�Ρ�

?Communication System Block Diagram

????????A2B��֡ͼ��ʾ����һ����ʼ��Ϊ���δ���,����Ϊ���δ���ij�֡��

A2B Superframe

??????? A2B�����ϵ������źŶ����б����,���ڵ���ͬ�����Ե���ʽ��ͬ���ź�����ת�������һ���ӽڵ㡣������Ժ����ǿ���֡(SCF)��������,TDMͬ������ֱ�������ڿ��ƿ�֮��ÿ�������ڵ㶼����ʹ�û�����һЩ��������,��Ϊ���νڵ��������ݡ����һ���ӽڵ�����Ӧʱ��֮������Ӧ֡(SRF)������Ӧ������ͬ��������ÿ���ڵ�����Ӧ֮֡��ֱ�����ӡ�ÿ���ڵ㻹����ʹ�û������������ݡ�����ͬ�����ݶ�����֯�ɵȿ������ݲ�,�������κ����β۵Ŀ��ȿ��Բ�ͬ����ϸ��Ϣ��μ�A2B��λ��ʽ��

??????? Ƕ��ʽ���ƺ���Ӧ֡����������A2B�����ϵ���Ѱַÿ���ӽڵ㡣�����Ƶķ�ʽ,���������Է���Զ����Χ�豸,��Щ�豸ʹ��I2C- to-I2CԶ����ͨ�����ӵ��κ��ѷ��ֵĴ��շ�����

????????A2Bϵͳ�е����нڵ���ͬһ��A2B��֡��ͬ����������վ��ͬ��I2S/TDM����������ͬһA2B��֡�е������д�վ,���ڵ��������Ƶ��������վ��ͬһI2S/TDM֡��ͬ�����ū��֮���ʣ����Ƶ��λ�����ͨ��ʹ��A2B_SYNCOFFSET�Ĵ�����ͬ�������ź��ӳٵļĴ����ɱ�̾�ϸ������������

????????����ÿ���������ڶ�ͨ��I2S/TDM�ӿڽ��պʹ�������,���������A2B���ߺ�I2S/TDM�ӿ�֮���ƶ������ӳ١�A2B����������֮���ʱ���ϵ��ͼA2B����ͬ�����ݽ���ͼ��ʾ��

?A2B����ͬ�����ݽ���ͼ

????????ע����A2B����ͬ�����ݽ���ͼ��,��������Ʒ���Խ���A2Bϵͳ�ij�֡����,������ʾ:

??????????????? 1������֡M�����ڵ��շ�����������ݲ�����������M��

??????????????? 2������֡N�дӽڵ��շ�����������ݲ�����������N��

??????????????? 3��A2B�շ�оƬͨ��I2S/TDM�ӿڽ��յ������������³�֡��ͨ��A2B���ߴ��䡣

??????????????? 4��A2B�����ϵ�����ͨ�����³�֡�е�A2BоƬ�շ�����I2S/TDM�ӿڽ��д��䡣

??????????????? 5��ͨ��A2B����(���ӻ����)�������������������֡���ӳ�,�����շ�оƬ�л��۵��κ��ڲ��ӳ�,�Լ����ڵ��߳�����ɵ��ӳ١����,��һ��A2B�շ�оƬ��I2S/TDM�ӿڵ���һ��A2B�շ�оƬ��I2S/TDM�ӿ�,��ʱ���Ը�����������֡��

3����������

????????A2B�շ����������Ӷ�·PCM (inter-IC����)ͬ��PCM (multi - channel I2S)����,�ڵ����봫��(���³����Բ�Ʒ����˵����Ϊ)��������I2S��ͬ����ʱ�ֶ�·����������չ��һ�����Ӷ���ڵ��ϵͳ,����ÿ���ڵ����ʹ�����ݡ��ṩ����,�������С�

????????A2B�շ���֧��A2B����Щ����,ͨ����·I2S/TDM�ӿ���ͨ�õ�dsp��fpga��asic����˷硢adc��dac����������Ƚӿ�������ͨ��A2B������·������������˹�ر���ġ����շ�������ȫ֧��ͨ��A2B��·����I2Cͨ�š�A2B�շ����ȿ������ڴӽڵ�,Ҳ�����������ڵ㡣Ĭ�������,�շ�������ʱΪ���շ���,���������������A2B_CONTROL.MSTR,���������Ϊ���շ�����

????????���Ľڵ�A2Bϵͳͼչʾ��һ����A2Bϵͳʾ��������������ÿ���ڵ�ע��,�Կ���A2B�����ϵ������������ӽڵ�0��2����˷������·�������,�ӽڵ�1��2�����������ݴ������·���dac��

���Ľڵ�A2Bϵͳ��ͼ

4���ܹ�����

????????���²����ṩ������Ӳ���顢�ӿںͻ�������Ϣ��

4.1��I2C�ӿ�

????????I2C�ӿ����ڴӱ������ӵ�����ֱ�ӷ����շ����Ĵ����ռ�,��ͨ��A2B���������շ�����ϵͳ���κη��ֵĴӽڵ�֮��Զ�̽���I2C���ݡ����Э�鱻��ΪI2C over distance,���н�����I2C���ݱ�Ƕ����ͬ������֡(����,������Ŀ���)��ͬ����Ӧ֡(����,��Ŀ��ӵ���)�С�

??????? ģ���е�I2C�ӿ�֧�����5v����ƽ,���������ص�:

??????????????? 1��A2B���ڵ��ϵ�Slave only������

??????????????? 2��A2B�ӽڵ��ϵ�����������Ӳ�����

??????????????? 3����A2B_I2CCFG.DATARATE���õ�100k��400kλ/s���ʵIJ�����

??????????????? 4��7λѰַ��

??????????????? 5��ʱ����չ��

????????????????ע��:���ڵ��ϵ�A2B��������֧��I2Cʱ����չ,�Ա������շ����ӿڡ�

????????������Ϊmaster���շ�������ʶ������I2C�豸��ַ:

??????????????? 1��BASE_ADDR:����ͨ��I2C�˿�ֱ�ӷ������ļĴ����ռ���

??????????????? 2��BUS_ADDR:����ͨ��A2B����ʹ��I2C over distanceЭ��Զ�̷��ʴӽڵ�Ĵ���

????????�ʹӽڵ�I2C���衣

????????I2C BASE_ADDR��ADR2/IO2��ADR1/IO1�������ϵ縴λʱ������������,�Ӷ�֧�����4�����豸���ӵ�ͬһ��I2C���ߡ�7λ�豸��ַ��LSB����I2C���ݽ�����ʹ��BASE_ADDR(λ1 = 0)�����շ���,����ʹ��BUS_ADDR(λ1 = 1)ͨ��master-enabled���շ����������߽ڵ�,��I2C��ַ����ʾ:

?I2C�豸��ַ��

????????������Ϊslave���շ�������ʶ��BUS_ADDR���ڴ��շ�����,I2C�ӿ�����I2C������Ϊ�����շ���ͨ��A2B���߽��յ�����������Զ��I2C�����������ʱ,������I2C�����ˡ����շ�����ΪI2C����,Ȼ��I2C����ת��������A2B_CHIP�Ĵ����б�̵�I2C�ӵ�ַ���������ⲿ������ͨ��I2C�˿ڷ����շ��Ĵ���(BASE_ADDR)ʱ,����I2C slave��

????????ע��:�������ⲿ���������ԶԴ��շ����ļĴ����ռ���б��ʱ,A2B_SWCTL��A2B_RESPCYCS��A2B_SLOTFMT��A2B_DATCTL��A2B_RAISE��A2B_GENERR�Ĵ���������Զ������ͨ��A2B����д�롣�ӱ���I2C�˿�д����Щ�Ĵ����ԼĴ���û��Ӱ�졣

????????�շ����ϵ�I2C�ӿ��������������ǰ���мĴ�����̡�д1��ʾ����(W1A)λ(����,A2B_CONTROL.ENDDSC��A2B_CONTROL.NEWSTRCT)��������֮ǰ��Ч,��ΪЭ���������������С�

????????ע��:A2B_SWCTL, A2B_SLOTFMT, A2B_DATCTL��a2b_discry�Ĵ�������������֮ǰд�����շ���������������֮ǰ,����Щ�Ĵ�����д��������Ч�ġ�

????????ע��:ϵͳ��������Ʊ������ͬʱ��A2B����(ͨ��A2B����)�ͱ��ش�����(ͨ��I2C�˿�)д��ͬһ�ӼĴ�����������д����ʱ,����д�����������,����������ɵ�˳���Dz���Ԥ��ġ�

4.1.1��I2Cʱ����չ:

????????�շ�������I2Cʱ����������,��֤I2C�������㹻��ʱ�䴦������ҪӦ��������I2Cͨ��A2B���߽���ӽڵ��շ����ʹӽڵ�I2C���衣ʱ������������������ʱ����Ӧ����I2C���ʷ���:

??????? 1����д�����ڼ� - - ��ÿ�������ֽ�֮���ȷ��λ֮ǰ��

??????? 2���ڶ������ڼ� - - �ڶ���������ȷ��λ֮ǰ��

??????? 3���ڶ�һ�������ֽڵ�ͻ����/д�����ڼ� - - �ں��������ֽڵĵ�һ������֮ǰ��

????????��SCL�ź����������������շ�����Ҫ�����ʱ������������һ���շ�������Ӧ������,���ͻ���SCL�ź�����,���������Ϳ������»�ö�SCL�Ŀ���,������Ӧ��(ACK)����һ���ֽڡ�

??????? ע��:��A2Bϵͳ�����,����(I2C����)����֧��I2Cʱ����չ��

????????���ӽڵ��е���Χ�豸����I2Cʱ��ʱ,SCL�ź�Ҳ�����շ���������֮�����������SCL�ź���32������֡��ʱ����û�б���Χ�豸�ͷ�,������ע��һ����ʱ(A2B_INTPND2��I2CERR = 1),�ͷ�SCL,��ֹͣ������ʱ�ӵ����졣�����ʱȷ������Χ�豸����ʹ������I2C�ӿ�����ֹͣ��

4.1.2������I2C�շ���

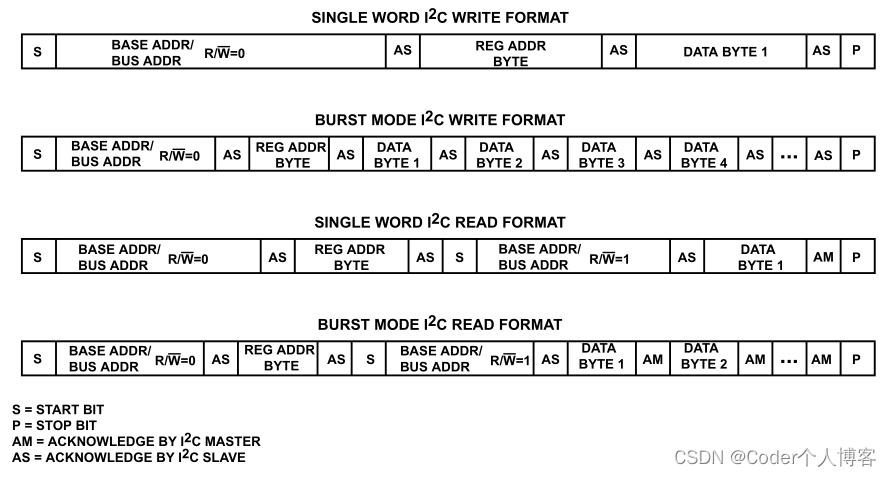

????????7λ�豸��ַ��LSB����I2C���ݽ�����ʹ��BASE_ADDR(λ1 = 0)�����շ�������ʹ��BUS_ADDR(λ1 = 1)ͨ�������õ��շ����������߽ڵ�,���±���ʾ��

?I2C�豸��ַ

????????A2B�շ���֧�����¶�д����:

??????????????? 1������д��������A2B��(I2C��)�ڵھŸ�ʱ�������ڼ�����SDA����ȷ��,�Ӷ����

????????���ʡ�

??????????????? 2��ͻ��ģʽд�����С����շ�����ÿ�������ֽ�֮���Զ����ӼĴ�����ַָ��,��˿�

????????���ڲ����±�̵�ַ�������д��˳�����ݼĴ�����

??????????????? 3�����ֶ���������һ����дλΪ0,��ʾд������������Ϊ����д��Ĵ�����ַ������

????????�ڲ���ַ����I2C�Ӷ�ȷ���յ��Ĵ�����ַ��,I2C���˱��뷢��һ���ظ�����������,���

????????��R/Wλ��Ϊ1(��)��оƬ��ַ�ֽڡ����I2C������SDA����,����ʼ������������I2C��

????????����Ȼ��I2C������ÿ��9������������������һ��ȷ�����塣

??????????????? 4��ͻ��ģʽ��ȡ���С����շ�����ÿ�ζ�ȡ�����ֽں��Զ����ӼĴ�����ַָ��,���

????????����Ե�ַ���±�̾Ϳ��Զ�ȡ���������ݼĴ�����

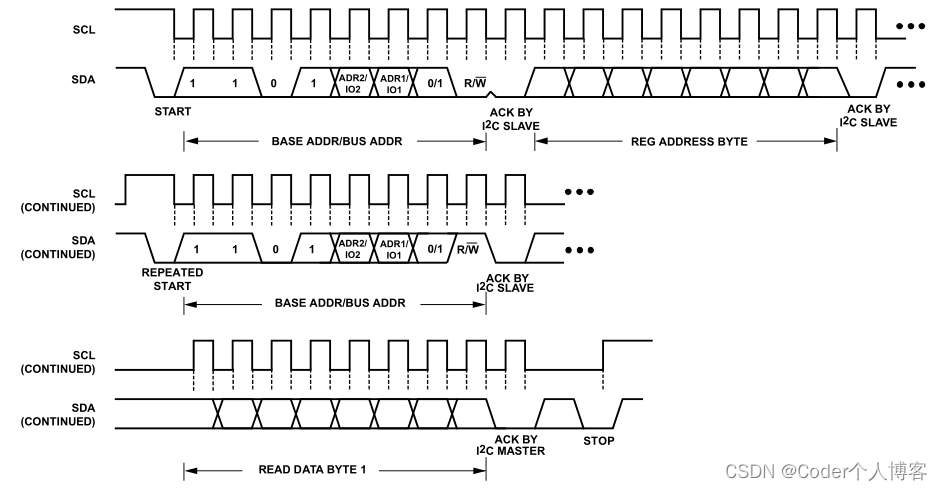

????????ͨ��I2C�ӿڴ���������Ҫ���²���:

??????????????? 1�����ݴ��������ӵ�A2B�շ���������������

??????????????? 2������������һ����������(SDA�ϴӸߵ��͵�ת��,��SCL���ָ�),�����һ����

????????ַ/���������

??????????????? 3���ڽ�������8��SCL������,A2B�շ���������(������MSB)���յ�һ��7λ��ַ��

????????R/W�

??????????????? 4��A2B�շ���ʶ�����ַ,���ڵھŸ�ʱ������(ȷ��λ)�ڼ����������߽�����Ӧ��

????????R/Wλ���������ݵķ�����һ���ֽڵ�LSB�����(=0)ʱ,����������д����Ϣ������һ���ֽڵ�LSB������(=1)ʱ,������������ȡ��Ϣ��ֱ������ֹͣ����(��SCL���ڸ�λʱ,SDA�ӵ͵�ƽת�����ߵ�ƽ)���ݴ���Żᷢ�����Ĵ�����ַָ���Զ�����,��֧�ֶ����ʹ�ͻ��ģʽI2Cд��ͻ��ģʽI2C����

????????I2C������ʽ����ͼ��ʾ:

??????????????? 1��д��BASE_ADDR/BUS_ADDR������һ�������ֽڵ����ݡ��豸��ַ��ĵ�һ

????????���ֽ������豸�еļĴ�����ַ�������ֽڱ�д�뵽Ѱַ�Ĵ��������ڵ�ַָ����ÿ��д

????????������,��˿����ڵ���������д��˳��Ĵ�����

??????????????? 2����BASE_ADDR/BUS_ADDR��ȡ�����ݿ�����һ�������ֽڵ����ݡ�����дָ

????????ʾ���豸��ַ������Ÿ��豸�еļĴ�����ַ�ʹ��ж�����ָʾ���ظ��豸��ַ��

I2C���ݸ�ʽ

????????�ظ����豸��ַ��ĵ�һ���ֽڰ�����Ѱַ�ļĴ�����ֵ���豸��ַ��ĵ�һ���ֽ������豸�еļĴ�����ַ�����������ظ����豸��ַ,�����ж�����ָʾ�������ֽڰ����Զ����ӵļĴ�����ַ��ֵ��

?I2C��дʱ��ͼ

??I2C�Ķ�ʱ��ͼ

4.1.3��Transceiver I2C Access Latencies

????????��I2Cͨ��A2B����Զ�������Զ���շ���ʱ,������ӳ١���I2C����ʱ�ӡ����и����˲�ͬ����I2C�����A2B����ʱ�ӡ�

????????I2C�����ӳ�(48khz��֡��)

| I2C Access Type(Conditions) | Estimated A2B Bus Latency (��s) |

|---|---|

| I2C������շ����Ĵ���д��N�������ֽ� (ʱ����չͨ����A2B_I2C.CFGEACK = 0���á�) | N �� 22 |

| I2C�Ӵ����շ����Ĵ�����ȡN�������ֽ� (ʱ������ͨ����A2B_I2CCFG.EACK = 0���á�) | N �� 22 |

| I2C����շ����Ĵ���д��N��>1�������ֽ� (ͨ������A2B_I2CCFG����ʱ�����졣EACK = 1,����I2Cʹ��400khz���������ʡ�) | 2 |

| I2C������շ����Ĵ���д��N�������ֽ� (ʱ������ͨ����A2B_I2CCFG���á�EACK= 1,����I2Cʹ��100khz����������) | 0 |

| I2C��Զ��I2C����д��N�������ֽ� (��A2B_I2CCFG.DATARATE = 0 = 100 kHz) | ((N �C 1) �� 113) + 213 |

| I2C��Զ��I2C����д��N�������ֽ� (��A2B_I2CCFG.DATARATE = 1 = 400 kHz) | ((N �C 1) �� 45) + 70 |

????????����,��������һ�����:����д��һ��Զ����Χ�豸(���ӵ��ӽڵ�)�Ĵ�������I2C����ʱ�ӡ�������I2C����ʱ������ɫ��ͷ��ʾ

??????? Note:I2C���������ӳٱ����������ӳ������û�г�ͻ�ķ��ʡ����I2C��Ϣû�������õ�

????????ȷ��,��������GPIO�жϡ���·�����жϡ�I2C����(NACK)�ȸ����ȼ��¼������ӳ�,����

????????����ִ����Ϣ����֮ǰ�������ӳٲ������ڱ����ṩ��ֵ�С�

4.2�������ܶȵ��ƽӿ�(PDM)

????????�����ܶȵ�������sigma�任����PDM��ʽ��ʾ��ȡǰ�Ĺ�����1λ�� �� ADC�ź�,ͨ������������˷�������ʽ��

????????PDMģ��֧�ָ߶�̬��Χ����˷�,���и������(SNR)����չ�������ѹ��(SPL)��

????????���շ�������ǿPDMģ��֧�ֱ�AD241x�շ������͵������ײ㡣�ṩ����120db������ȡ��շ����ϵ�PDMģ��֧��24 kHz��12 kHz������,����,ʹ����ͬ��PDMʱ������(��48 kHz֡������Ϊ3.072 MHz),��֧��48 kHz�����ʡ��շ���PDMģ���еĸ�ͨ�˲�����ֹƵ�ʹ̶�Ϊ1hz,���ɱ�̡���ͨ�˲�����һ��IIR�˲�����

????????�շ����ɱ��1x, 1/2x��1/4��PDM����(48 kHz, 24 kHz��12 kHz����)����ڳ�֡����(48 kHz����)������1/2x��1/4x PDM����,A2B����е�ͬ�����ݱ�����,��ƥ�䳬֡���ʡ������շ����Ľ�������������˽��ʹ��ʱ,�������͵�PDM���������ǿ��ܵ�(����,���͵�375����)��

????????�շ�����PDMλʱ�����Ƶ�ʱ�PDM��Ƶ������(ͨ��Ϊ3.072 MHz,����48 kHz��PDM��Ƶ����)��64����

????????ÿ��PDM���õĽ�������Խ��ն������ͨ������Ƶ����(������)������һ��ͨ����ʱ���������й�,��һ����ʱ���½����йء�

????????PDM��ʹ��PDM����(A2B_PDMCTL)�Ĵ�������:

??????????????? 1����A2B_PDMCTL.PDM0EN = 1, DRX0/IO5�������ý���PDM����,BCLK������һ

????????�����,ͨ��ΪTDM2���ò���3.072 MHz��ʱ�ӡ���ģʽ��DRX0/IO5�������ݲ����ݵ�I2S

????????/TDM�ӿڡ�ͬ��,A2B_PDMCTL>PDM1ENλ����DRX1/IO6�����ϵ�PDM���ݽ��ա�

??????????????? 2��A2B_PDMCTL.PDMxSLOTSλѡ��DRX�����ϵ�PDM�ź���ʹ��һ��(������)����

????????����(������)ͨ����

4.2.1��������˷��PDM������Ե

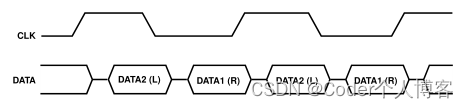

????????�����ܶȵ���(PDM)�ӿ���������������˷��PDM����ʹ�õ���ʱ���ڵ����������Ͻ���ʱ���·���á�

????????PDM��˷�����ݽ��б���,ʹ��ͨ����ʱ��(CLK)�źŵ��½�����Ч,����ͨ����CLK�źŵ���������Ч����CLK�źŵ��ʵ���������DATA�źź�,��˷��������̬�������,������˷�(һ�����������ͨ������һ���������ұ�ͨ��)���Թ���һ��������(��������PDM��ʽͼ)��

����PDM��ʽ

????????���շ�����,PDMģ�������64��ʱ�ӱ�Ե�ϵ���˷����ݽ��в������շ������뱻���Ϊÿ֡����64��BCLKs��TDMģʽ(Ĭ�ϵ�TDM2/32��TDM4/16ģʽ)��TDM���ò�Ӱ��PDM�顣

????????���շ�����,��BCLK�����زɼ����������ǵ�һ�ŵ������A2B_PDMCTL.PDM0SLOTS=1��A2B_PDMCTL.PDM1SLOTS = 1,��һ����λ��BCLK���������,�ڶ�����λ��BCLK�½�����ء�

????????����,�ӽڵ��DRX0/IO5��DRX1/IO6���ŷֱ�����������˷�,PDM0��PDM1��λ����Ϊ2��λ�������������,PDM���ÿ֡64λ�����ݽ��в���,����ת��Ϊ24λ��PCM����,������ת��������,������ʾ:

??????? 1���Ҳ���˷�����������ʱ�ӱ�Ե��DRX0�����ϲ���,��������A2B�����ϵĵ�һ*�����ۡ�

??????? 2�������˷��������½�ʱ�ӱ�Ե��DRX0�����ϲ���,��������A2B���ߵĵڶ�*������С�

??????? 3���Ҳ���˷�����������ʱ�ӱ�Ե��drx1�����ϲ���,��������A2B���ߵĵ���*�����ۡ�

??????? 4�������˷��������½�ʱ�ӱ�Ե��DRX1�����ϲ���,��������A2B���ߵĵ���*������С�

??????? ע��:����*Ϊʵ�ʲ�λ��,�����ϵͳ��λ������д��

????????��ʹ��Ĭ�ϵ�A2B_PDMCTL2����ʱ,PDM���������������������ݽ��в���;���,A2B_I2SCFG.RXBCLKINV��A2B_I2SCFG.PDMģʽ������TXBCLKINVʱ�ӷ�ת����ʱ����TXBCLKINVʱ�ӷ�ת���á�

????????���ʹ��Ĭ�ϵ�A2B_PDMCTL2���ú�A2B_PDMCTL.PDM0SLOTS = 0��A2B_PDMCTL����PDM1SLOTS = 0ʱ,ֻ����ȷ��ͨ��������PDM�����ϲ��������ֻϣ�������ͨ�����ݽ��в���,����ͨ������A2B_PDMCTL��֧�֡�PDM0EN = A2B_PDMCTL.PDM0SLOTS = A2B_UPFFSET = 1��

4.2.2��PDM��ǿ

????????Ĭ�ϵ�PDM������ȫ��������ǰ���շ�����;����,���м�����������ʹPDM�ӿڸ�����

4.2.3��PDMʱ��ѡ��

????????DRX0��DRX1�������ſ��Ե�������ΪPDM���롣����һ��������DRX���ŵ�A2B�ӽڵ�������PDM�ӿ�ʱ,��Ҫ����64 �� fSYNCM(��48 kHz fSYNCM��3.072 MHz)��PDMCLK�ź���ʱ��PDM�豸���շ�������PDMCLK/IO7��BCLK�������������PDMCLK��IO7�ϵ�PDMCLK����ͨ������A2B_PDMCTL2.PDMALTCLK�����á�

????????���ʹ��PDMCLK/IO7������BCLK,��TDM2/32��TDM4/16�����ƽ���ɾ����BCLKƵ�ʿ���ͨ��I2S/TDM�Ĵ�������Ϊ��ͬ��Ƶ�ʡ��ڱ�����,PDMCLK/IO7���ڲ���DRX0/DRX1�ϵ�PDM���롣

????????BCLK��PDMCLK/IO7Ҳ����ͬʱʹ��,����ͬ��Ƶ�ʺ���λ����,�������෴��PDM��˷�ʱ�ӡ�����ͨ������A2B_PDMCTL2����ɵġ�PDMALTCLK������,�Ĵ����������Ȳ������������ݻ����½�������:

??????????????? 1����A2B_PDMCTL2.PDM0FFRST = 0(Ĭ��),DRX0�ϵ�PDM0�������ȴ�������Ե

????????��������A2B_PDMCTL2.PDM0FFRST = 1ʱ,�ȶ��½��ؽ��в�����

??????????????? 2����A2B_PDMCTL2.PDM1FFRST = 0(Ĭ��),DRX1�ϵ�PDM1�����ȴ�������Ե��

????????������A2B_PDMCTL2.PDM1FFRST = 1ʱ,�ȶ��½��ؽ��в�����

??????? ע��:�����ڵ���,BCLKʼ����һ������;���,���ӵ����շ�����PDM��˷��ʱ�����ͨ������PDMCLK/IO7��

4.2.4��PDM����·��ѡ��:

????????PDM�ӿڿ��������շ�������շ������շ������յ���PDM���ݿ��Է��͵�A2B�����ϵ��κνڵ�,Ҳ���Է��͵����ص�I2S�˿�,����ͬʱ���͵�A2B�����ϵ��κνڵ㡣����ʹ��A2B_PDMCTL2.PDMDEST�ֶ���ɵġ�

4.2.5��ȫ˫��I2S���ĸ�PDM��˷�:

????????���ͬʱʹ����������(DRX0��DRX1)����PDM����,����Ըı�DTX1�Ĺ���,ʹ����Ϊ����DRX1,ʵ�����4��PDM��˷�IJ���ʹ�ú�ȫ˫��I2Sͨ�š�����ͨ������A2B_I2SGCFG.RXONDTX1��ɵġ�

4.3��I2S/TDM�ӿ�

????????I2S/TDM���ڹ�����ȫ˫��ģʽ��,���Ͷ˺ͽ��ն�ʹ����ͬ�Ĺؼ���ʱλʱ��(BCLK)��֡ͬ��(SYNC)�ź�ͬʱ������A2B�Ӷ��շ�������I2Sȫ�����üĴ���(A2B_I2SGCFG)��I2S���ʼĴ���(A2B_I2SRATE)��I2S���ټĴ���(A2B_I2SRRATE)��������BCLK��SYNC����ܽ��ϲ���Ƶ�ʶ�ʱ�źš�A2B���շ���ʹ����ͬ��BCLK��SYNC������Ϊ����,����������,�Ӷ��ṩ��������A2B�������˵�ʱ����

4.3.1��ʱ�ֶ�·����Э��

??????? TDMģʽ��I2S�ӿ���չ����ֹһ��������2ͨ��(TDM2)�źš�����A2B_I2SCFG�Ĵ����ж��շ��������֧��һ��������TDMͨ��ʱ,��������TDMͨ����ÿ�����õ�I2S/TDM��������(DTX0��DTX1��DRX0��DRX1)���ǿ��õġ�֧��TDM2��TDM4��TDM8��TDM12��TDM16��TDM20��TDM24��TDM32ģʽ��

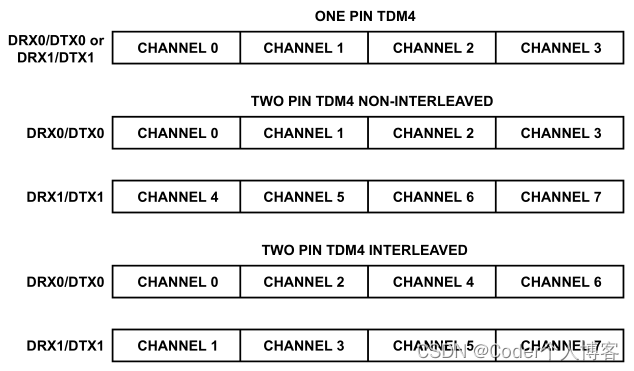

????????����,ѡ��TDM4,ʹ��һ������pin (DTX0),����4����������ͨ�������ѡ��TDM4,ͬʱʹ��DTX1��DTX0,����8����������ͨ��,��ͼ��TDM4��������ͨ���ṹ����ʾ

?TDM4���õ�����ͨ���ṹ(TDMMODE == 001)

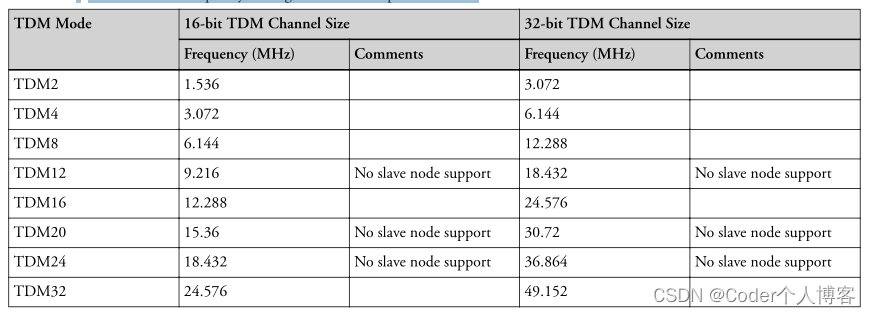

????????I2S/TDM����֧��16λ��32λ����ͨ������,�ɳ��ر��ֳ��źš�������������MSB��һ��ʽ��ʾ����ͬʱ�ָ���ģʽ��BCLK�ź�Ƶ����I2S/ʱ�ָ���ʱ��Ƶ������48khz��֡�ʱ�����ʾ��

I2S/TDMʱ��Ƶ������Ϊ48khz����֡��

????????DRX0��DRX1�������ſ��Ե�������ΪPDM���롣����һ��������DRX���ŵ�A2B�ӽڵ�������PDMʱ,PDM�豸��Ҫ����64 �� fSYNCM(��48 kHz fSYNCM��3.072 MHz)��PDMʱ�ӡ�PDMCLK/IO7���Ż�BCLK���Ŷ��������������PDMʱ�ӡ��շ��������ڽ���PDM����ͬʱ,ͨ��DTX0��DTX1���Ŵ���TDM���ݡ���ʹ��BCLK��ΪPDMʱ��ʱ,��֧��I2S/TDM2��32λͨ�����Ȼ�16λͨ�����ȵ�TDM4��ʹ��PDMCLK/IO7������BCLKʱ��PDM�豸I2S/TDM�ӿ�����BCLK���ڸ���TDMģʽ�����ͬʱʹ��DRX0��DRX1����PDM����,����Ըı�DTX1�Ĺ���,ʹ��䵱����DRX1����ʹ��������ͬʱʹ��4��PDM��˷��ȫ˫��I2Sͨ�š�

????????���PDMֻʹ��һ������(DRX0��DRX1),��һ�����ſ�ͬʱ����I2S/TDM���䡣

4.4��Mailboxes

????????��������������MBOX0��MBOX1,�������������ʹӽڵ���ƴ�����֮��Ĵ�������ͨ�š�

????????ע��:�ڱ�����,��MBOX0�������ض�����ҲӦ����MBOX1ʵ�����ӽڵ��еĴ���������ͨ��I2C��A2B���շ����еļĴ���������Ϣ�������ڵ���,���շ�����IRQ/IO0�����ϵ��ж�֪ͨ��������������Ϣ,������ʹ��BUS_ADDR��I2C�ϵ�A2B���շ����Ĵ���������Ϣ�����������Ϣ�����Ǵ�A2B���ڵ㵽A2B�ӽڵ�,����ʹ��BUS_ADDR��I2C�ϵ�A2B���շ����Ĵ����з�����Ϣ���ڴ����ڵ���,������ͨ�������շ�����IRQ/IO0���ŵ��жϵõ���������Ϣ,�������ڼ��A2B_LINTTYPE�Ĵ�����,ֱ��ͨ��I2C��A2B�����շ����Ĵ�������������Ϣ��

4.4.1�������������

????? A2B_MBOX0CTL�Ĵ����ṩλ�ֶ�����������Ϳ��Ʒ�����Ϣ���Ⱥ��жϹ��ܡ�

????????Ĭ�������,����0������Ϊ��������(������д��,�ӽڵ㴦������ȡ),����1������Ϊ��������(�ɴӽڵ㴦����д��,������ȡ)������A2B_MBOX0CTL��MB0DIRλ��������ķ���

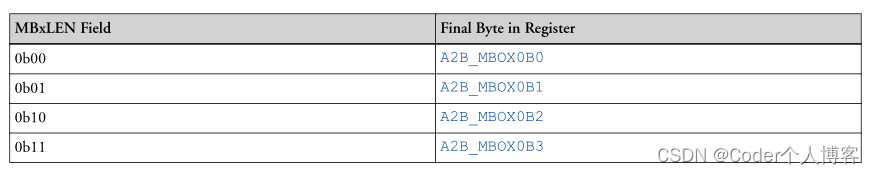

????????ÿ�������������8��16��24��32λ��Ϣ,����A2B_MBOX0CTL�����õ�������MB0LEN�ֶΡ����ֶ��е�ֵ����ʹ���ĸ��ֽڷ�Χ��A2B_MBOX0B0��A2B_MBOX0B3�Ĵ����е��ĸ��Ĵ������洢����,���е�һ���ֽ�������A2B_MBOX0B0�Ĵ�����,���һ���ֽ�λ�����ɱ�����ݳ��������������ݼĴ�����,���±���ʾ��

?????????���������õĽ�������(A2B_MBOX0CTL��MB0EN = 1��A2B_MBOX0CTL.MB0DIR = 0),���������A2B_MBOX0CTL.MB0FIENλ,��������д����������һ���ֽڲ���A2B���շ������պ�,�ӽڵ㷢���жϡ����������A2B_MBOX0CTL.MB0EIENλ,�жϻ���������ȡ��������һ���ֽں�,ͨ��A2B���������δ����������ӽڵ��еı��ش�������

????????���������õĴ�������(A2B_MBOX0CTL.MB0EN = 1��A2B_MBOX0CTL.MB0DIR = 1),���������A2B_MBOX0CTL.MB0FIENλ,��ô�ڴӽڵ��еı��ش�����д����������һ���ֽ�֮��,�ͻᷢ�����������жϡ����������A2B_MBOX0CTL.MB0EIENλ,����������ȡ��������һ���ֽں�,�ж�ͨ��A2B�������´����������ڵ㡣

????????ע��:��̬�������������õ�����(A2B_MBOX0CTL.MB0EN = 1)����ֹ�������������Ƚ�������(A2B_MBOX0CTL.MB0EN = 0),�����Ҫ��������,�������������ķ�����������������

??????? �����䱻����ʱ,A2B_MBOX0STAT�Ĵ����ṩ�����״̬��Ϣ:

??????????????? 1��������MB0FULL����A2B_MBOX0STAT.MB0EMPTY�

??????????????? 2����һ�����䱻���,A2B_MBOX0STAT��������MB0EMPTYλ�����

????????A2B_MBOX0STAT.MB0FULL�

??????????????? 3���������������ش����������ж��ź�ʱ����A2B_MBOX0STAT.MB0EIRQ��

??????? A2B_MBOX0STAT.MB0FIRQλ���������ش����������ж�ʱ�����Щλ��

????????����ӽڵ����ͨ�����ǵ�TX���������ڵ�ͨ�š������ڵ���,A2B_INTTYPE�Ĵ��������κδӽڵ�������ݹ��жϵ���Ϣ,�ӽڵ���A2B_INTSRC�Ĵ����б�ʾ��

????????����������������ͬʱ�����ǵ�����д�ʼ�ʱ,�������������������Ĵ�������������õ��ж�ָʾ���ڼ��жϺ�,����ͨ����ȡA2B���շ������ж�����(A2B_INTTYPE)���ж�Դ�Ĵ���(A2B_INTSRC)����ȡ�ж���Ϣ,�ֱ�ȷ���ĸ��жϷ�����,�ĸ��ӽڵ�������жϡ��ڶ�ȡA2B_INTTYPE�Ĵ���ʱ,�ӽڵ��ϵ�A2B_INTSRC�Ĵ����е��ж����������IRQ/IO0�����л���ȥ����״̬,Ȼ������������һ���ӽڵ����Ȼ��Ծ���ж϶������ص�����״̬,�������������ٴζ�ȡ���շ�����A2B_INTTYPE��A2B_INTSRC�Ĵ�����ȷ����һ���ӽڵ�������жϡ�

4.4.2�������ӳ�

??????? ����������I2C�����ϵļĴ�����д��ɡ��ӷ������������������ж�������SRF����һ����,��˴ӷ���������������ӳٿ��ܰ���һ������ij�֡�ڵȴ����ʱ�䡣

????????��ͼ��ʾ���������������������ϵ�ϵͳ��ʱ��dz��ɫ��λ��ʾSCF��,���ɫ��λ��ʾSRF����

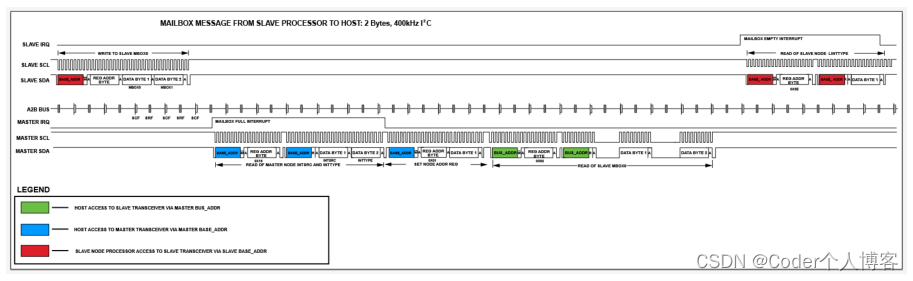

????????�������ӳ�(������������)ͼ��ʾ,��������Ϣ���������͵�����������ʱ,����������ʹ�ö����շ���BUS_ADDR�豸��ַ��2�ֽ�ͻ��д����,ͨ��SCF�ֶν���������д��A2B�����ڵ㡣��д�����ʱ,���շ����������䱾�ؽڵ㴦���������жϡ����,��IRQ/IO0�϶��Ե�slave�ж�����(slave IRQ)��SCF�ֶζ��롣һ������жϱ�����,�������ӵĴ���������ʹ�ô��շ���BASE_ADDR�豸��ַ��ѯ��A2B_LINTTYPE�Ĵ���,��ȷ������������ȫ�ж�,Ȼ��������ʹ��һ��2�ֽڵ�ͻ����ȡ���������ݼĴ�����ȡ���ݡ�һ����Щ�������,�����ڵ�(master IRQ)������������ж�,����SRF�ֶζ���,Ȼ������������ȡ���շ�����A2B_INTSRC��A2B_INTTYPE�Ĵ���(ʹ�����շ���BASE_ADDR�豸��ַ),��ȷ��������ָ���Ĵӻ������������ж�

�����ӳ�(��������Slave)

????????���Ƶ�,�������ӳ�(��Slave��Host)ͼ��ʾ,��������Ϣ�ӴӴ��������͵�����ʱ,�ӽڵ㴦������ʱͨ��ʹ�ô��շ���BASE_ADDR�豸��ַ��Ĵ�������д����������������ݼĴ���,����A2B�ڵ㷢�����ж�ָʾͨ��SRF�ֶΡ����,��IRQ/IO0�϶��Ե���������ȫ�ж�����(master IRQ)��SRF�ֶζ��롣һ������жϱ�����,����(ʹ�����շ���BASE_ADDR�豸��ַ)ѯ��A2B_INTSRC��A2B_INTTYPE�Ĵ���,��ȷ��������ָ���Ĵӻ����������ȫ�жϡ�

�����ӳ�(��Slave��Host)

????????���Ҫ�Ӵ����շ�������������ȡ����,�����������Ƚ�A2B_NODEADR�Ĵ�������Ϊ�����жϵĴ����ڵ�(ʹ�����շ���BASE_ADDRд����),Ȼ��BUS_ADDR��������ȡ�����շ��������������ֽڼĴ���(ע�ⷢ����Щ����������ij�֡���)��һ��������ȡ�����һ���ֽ�,�����ڵ�(slave IRQ)��������ж���������һ��SCF�ж��ԡ�Ȼ��,�ӽڵ㴦��������ʹ�ô��շ���BASE_ADDR��������ȡA2B_LINTTYPE�Ĵ���,����ȷ����������������ж�֮���ȡ�ж�(����,�ٴμ����������ݼĴ�����������������)��