Linux下Makefile操作

1.Makefile的作用

makefile 指的是一个叫 makefile 的文件,里面提前写了一些指令。每次要自动化的完成一个比较复杂项目的自动编译用的时候,就在命令行输入“make”命令。使用Makefile可以 “智能” 的知道:

- 哪些文件需要先进行编译。

- 当某一文件在某次make命令之后发生了改变。再一次使用make命令的时候Makefile只会针对变化的部分相关文件进行重新编译,而其他的不做任何改变,所以在效率上比较高。

2.Makefile的制作

- Makefile的文件名为“Makefile”或者“makefile”。

- Makefile的语法:

目标文件:依赖文件

命令

如:

app:add.c div.c sub.c mult.c main.c

gcc add.c div.c sub.c mult.c main.c -o app

这里app是我想生成的目标文件,而 add.c div.c sub.c mult.c main.c 是生成app所需要的文件。下面的命令则是表示“如何来生成app这个文件”。

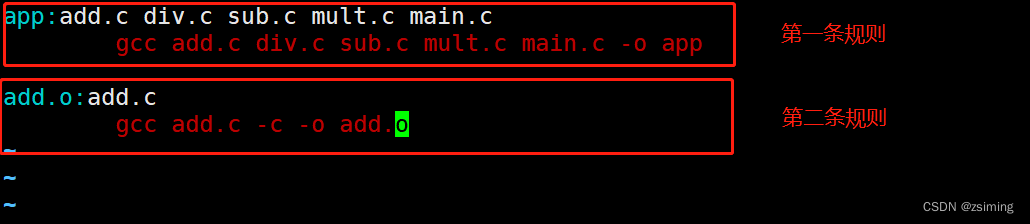

注意: 上面的例子总的称为“一条规则”。在Makefile文件中,下面可以添加其他的规则,而其他的规则都是为第一条规则而服务的,如果其他的规则与第一条规则毫不相关,那么则不会执行。举个例子:

app:add.c div.c sub.c mult.c main.c

gcc add.c div.c sub.c mult.c main.c -o app

add.o:add.c

gcc add.c -c -o add.o

上面的例子一共有两条规则,第二条规则是生成add.o文件。但是,第一条规则生成app文件的过程中,和add.o并没有任何关系,因此第二条规则是不会执行的。如图:

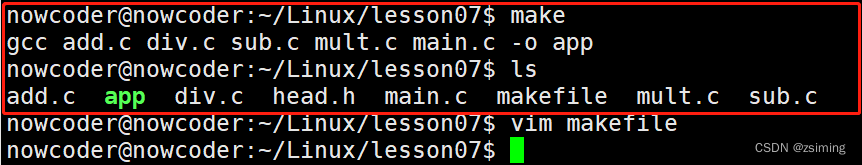

执行make命令之后:

可以看见,make 命令之后并没有执行第二条规则。而且用ls命令查看文件发现没有add.o文件生成。

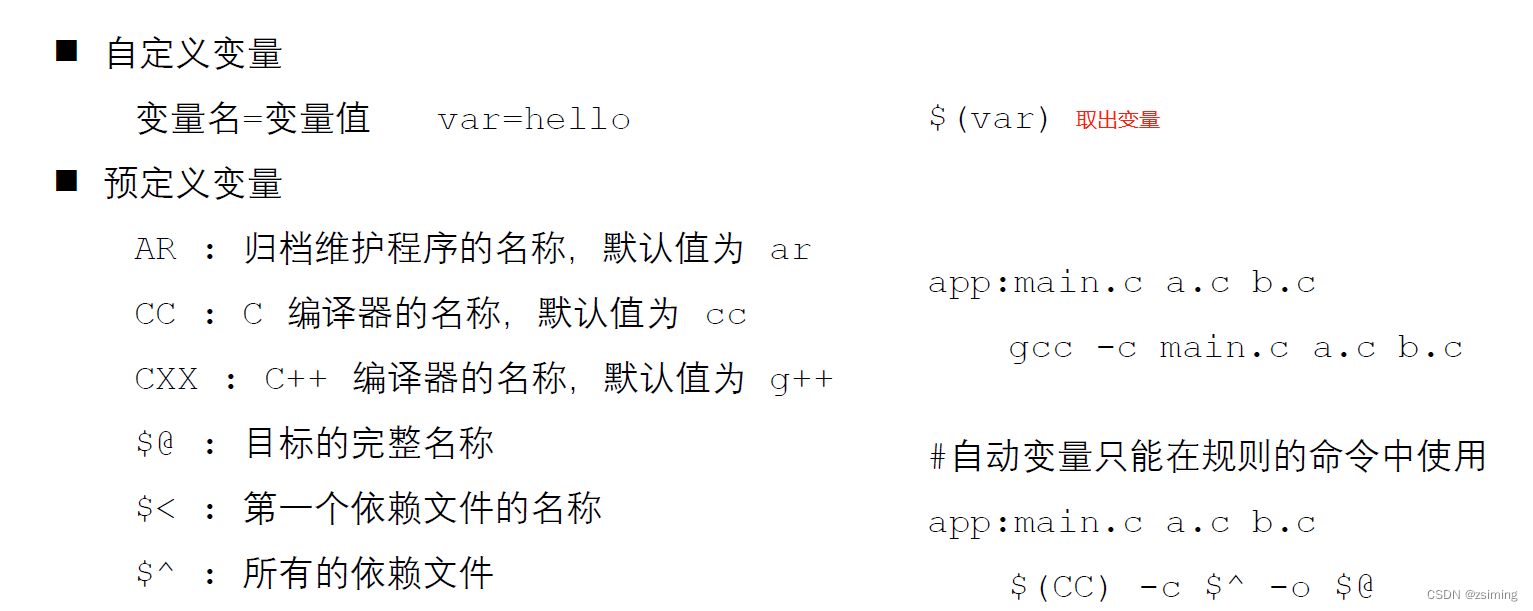

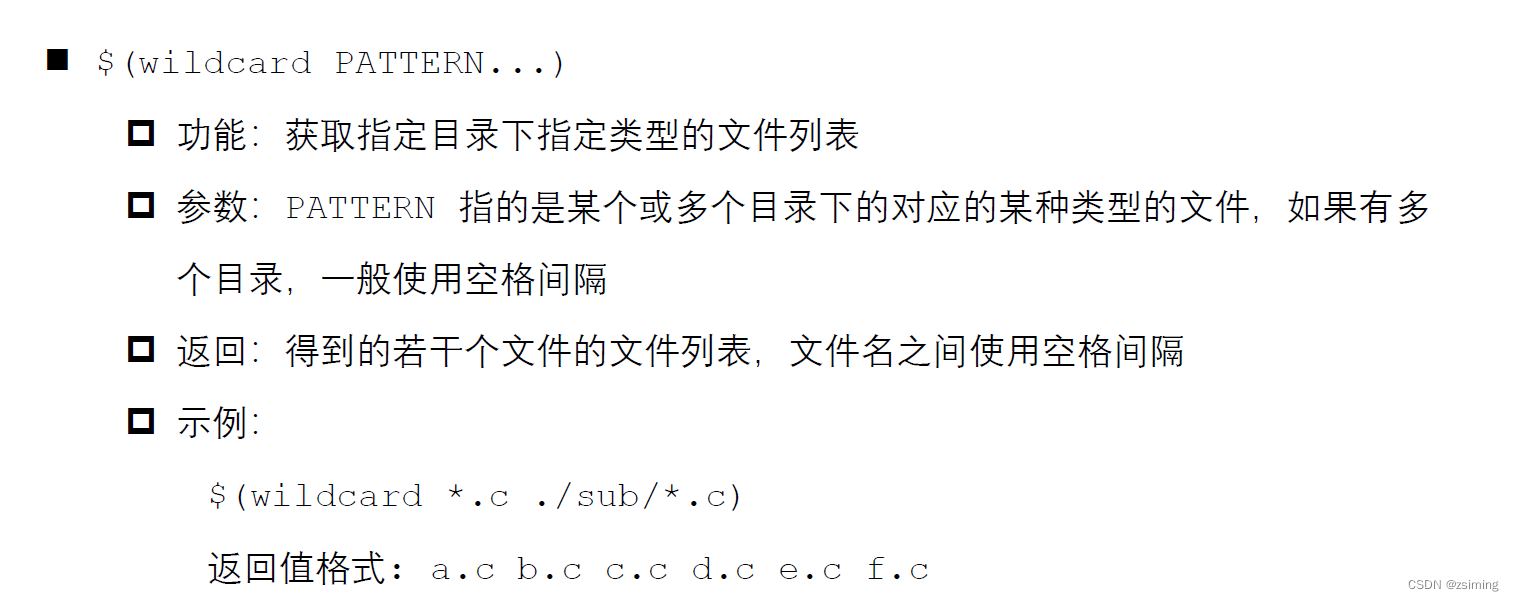

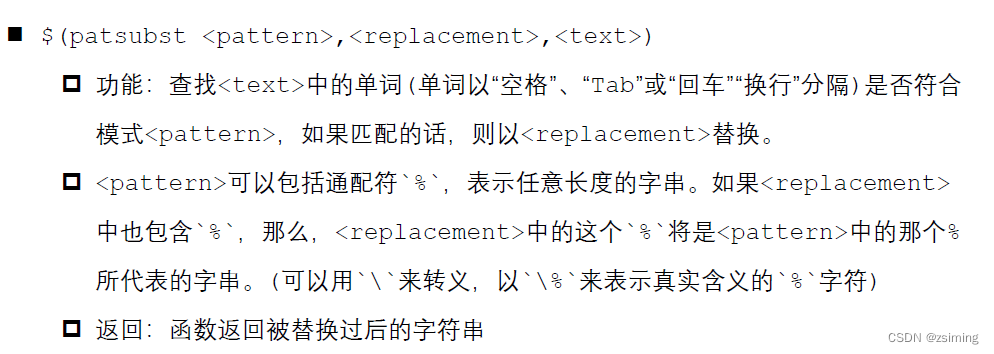

3.Makefile 偷懒方式

写Makefile文件的过程中,可以通过定义变量、使用函数的办法来少打一些命令和文件的名称。比如,在上面的Makefile 文件中,很多.c文件都是手打的,因此,我们可以通过函数的方式来获取这些.c文件的文件名,然后放在一个变量中,下次使用的时候,只需要使用变量就可以啦。

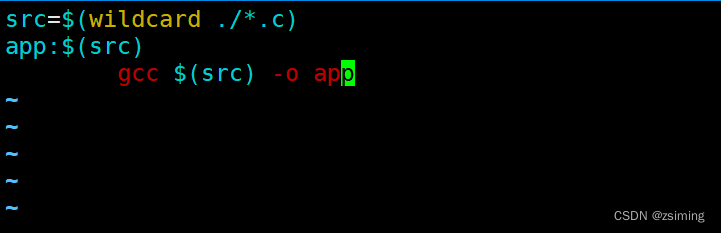

如下:

其中:

src=$(wildcard ./*.c)

函数$(wildcard)用来将某个目录下的某个类型的文件名全部取出来。这里就是将当前目录下的.c文件全部取出来,复制给变量src。而下一行的 $(src) 是将src的值取出来。

其他的一些常用变量、函数和通配符使用: